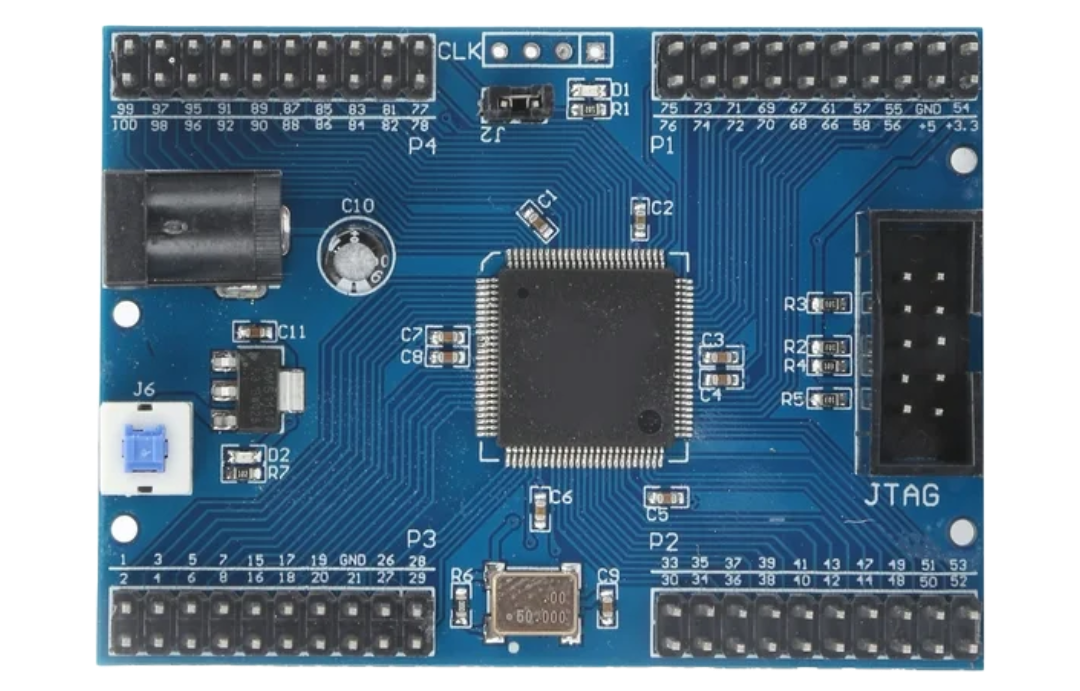

CPLD Altera U119 MAX II EPM240 con FPGA EPM240 + Programador Blaster

Tarjeta de desarrollo CPLD de alto rendimiento para prototipos y control digital.

Dispositivo

Voltaje de alimentación

Pines de entrada/salida

Memoria Flash

Placa de desarrollo

El CPLD Altera MAX II EPM240 es un dispositivo no volátil de alta fiabilidad diseñado para implementar lógica digital compacta y de baja potencia. Cuenta con 240 LEs (registers) que permiten crear máquinas de estado, controladores de motor y periféricos embebidos sin necesidad de reeditar hardware Intel. Su User Flash Memory de 8 Kbit facilita almacenar datos críticos y realizar actualizaciones en campo sin hardware adicional.

Con hasta 80 pines de usuario en paquete TQFP100/FBGA100, puedes configurar múltiples interfaces digitales (SPI, I²C, UART, GPIO) y soportar niveles I/O de 1.5 V, 1.8 V, 2.5 V y 3.3 V para interoperar con distintos periféricos. Internamente, un regulador lineal genera el voltaje de núcleo de 1.8 V a partir de la alimentación externa, garantizando estabilidad térmica y eléctrica.

La programación se realiza mediante JTAG utilizando el cable USB‑Blaster (compatibilidad USB 2.0 High‑Speed, RoHS), que permite descargar diseños con Quartus II a velocidades de hasta 10 Mbit/s aprox. directamente desde un puerto USB estándar Intel. Este esquema simplifica el flujo de trabajo de diseño, eliminando la necesidad de fuentes de programación aparte y facilitando la depuración de señales JTAG.

Ideal para ingenieros de sistemas embebidos, laboratorios de educación STEM y proyectos DIY, el EPM240 ofrece un equilibrio óptimo entre densidad lógica, consumo de energía (típico inferior a 100 mW en reposo) y facilidad de uso. Además, su ciclo de vida extendido garantiza disponibilidad en el mercado hasta 2040, minimizando riesgos de obsolescencia.

Especificaciones técnicas

| Familia | MAX II CPLD |

| Dispositivo | EPM240 |

| Voltaje de alimentación | 5V DC |

| Voltaje lógico E/S | 3.3V |

| Elementos lógicos | 240 LEs |

| Número de IO E/S | 80 |

| Entradas/Salidas programables para operar a niveles lógicos | 3.3 V, 2.5 V, 1.8 V y 1.5V |

| Conector de programación | JTAG |

| Temperatura de funcionamiento | -40°C a 100°C |

| Dimensiones aprox. | 50mm x 70mm |